A

Fast MPEG-4 FGS Decoding Architecture for Memory and Power Constrained Embedded

Systems

(應用於記憶體及運算能力受限之嵌入式系統的快速

MPEG-4 FGS 可調節視訊解碼架構)

Introduction

- Recently, the host platforms of multimedia applications have shifted from high-performance and less-resource-constrained devices like TV and PC to computation and resource constrained mobile devices such as PDA or smart phone.

- MPEG-4 is the most suitable standard for providing multimedia applications on mobile devices. However, though MPEG-4 provides high quality, high compression rate video, and excellent streaming ability, the corresponding implementation issues are still complicated.

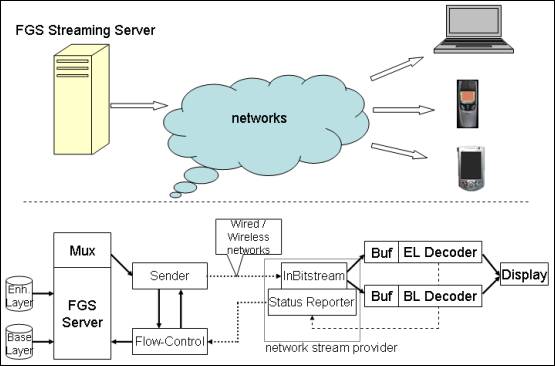

- A memory-efficient and power-constrained architecture for streaming and decoding MPEG-4 FGS video over embedded systems is proposed and implemented.

System

Components

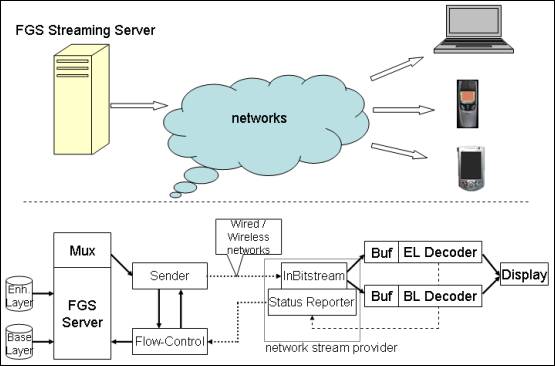

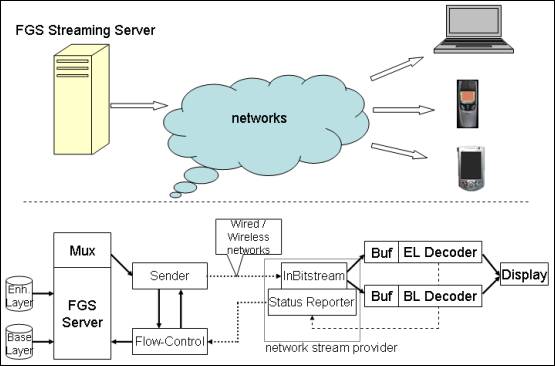

The objective of our system, streaming video to multi devices, including PC, smart phone, PDA, and TablePC, through heterogeneous networks, is achieved by combining three major components:

- FGS streaming server

- Client base layer decoder in compliance with the MPEG-4 simple profile

- Client enhancement layer decoder in compliance with the MPEG-4 FGS profile

Cross-Platform

Decoder Architecture

:Computation-bound components

:Computation-bound components

:

Memory-bound components

:

Memory-bound components

The

Macroblock-Sync FGS Decoding Architecture

The Macro-Sync FGS decoder can solve the main problems of FGS, for example, the extra need of large frame buffer and multiple memory scans and accesses.

Cache

Utilization of Macroblock-Sync Architecture

Reference

- His-Kang Tsao and Ja-Ling Wu, “An Efficient Macroblock-Sync Decoding Architecture for MPEG-4 FGS Video,” 45th IEEE International Midwest Symposium on Circuits and Systems.

- 曹希康,

“應用於記憶體及運算能力受限之嵌入式系統的快速 MPEG-4 FGS 可調節視訊解碼架構, ” 台大資訊所碩士論文.

![]() :Computation-bound components

:Computation-bound components

![]() :

Memory-bound components

:

Memory-bound components